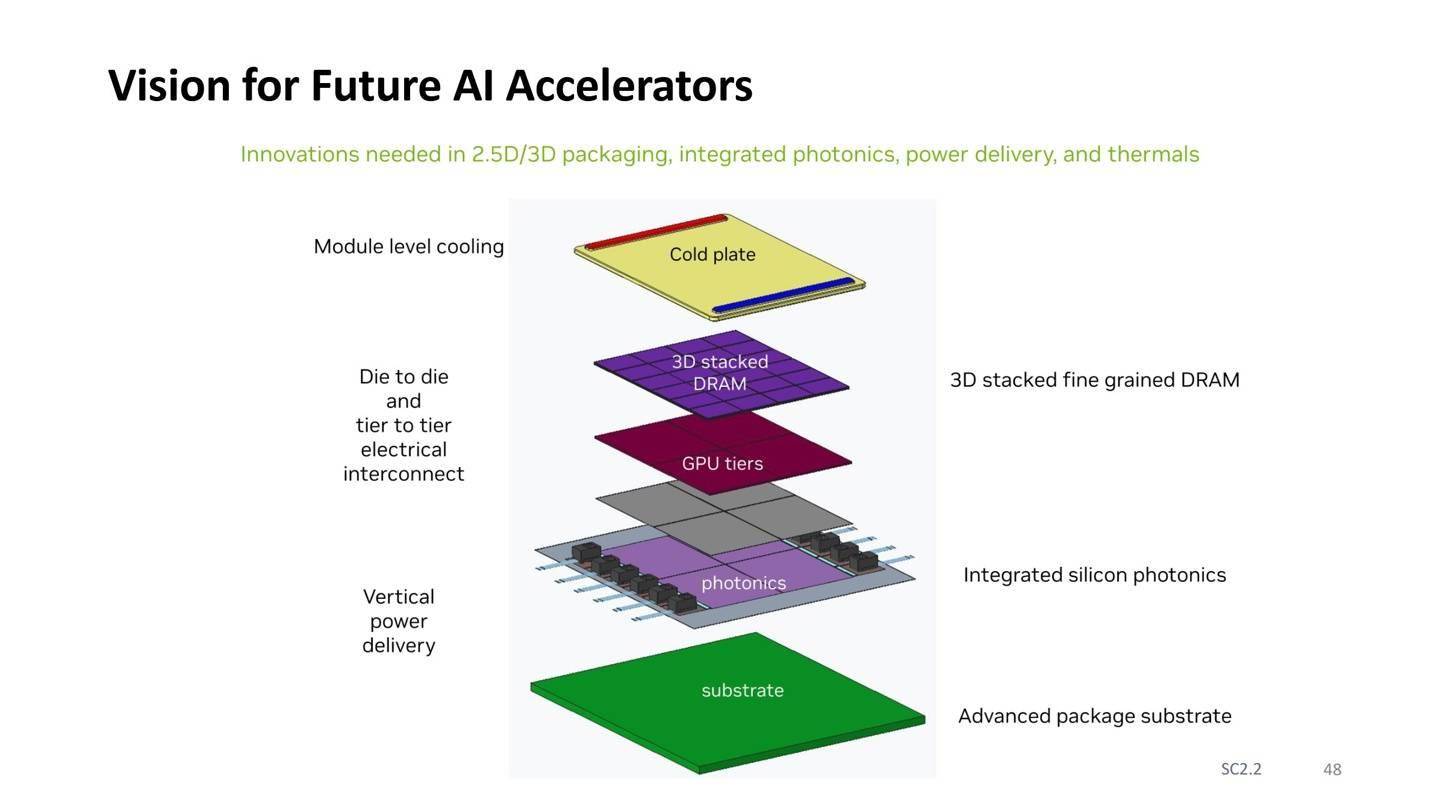

英伟达近期描绘了一幅未来AI加速器复合体的宏伟蓝图,该蓝图揭示了一种前所未有的技术集成方式。在这个设想中,AI加速器复合体将基于大面积先进封装基板构建,采用革命性的垂直供电设计,同时整合了硅光子I/O器件。

据透露,每个AI加速器复合体将包含四个GPU模块,这些模块通过垂直连接方式,与六个小型DRAM内存模块紧密相连,并且每个GPU模块都配备了三组硅光子I/O器件。这种设计不仅提高了数据传输带宽,还显著提升了能效。

硅光子I/O器件的应用是这一蓝图中的亮点之一,它超越了现有电气I/O的带宽和能效限制,成为未来先进工艺的重要发展方向。与此同时,3D垂直堆叠的DRAM内存方案相较于当前的2.5D HBM方案,具有更短的信号传输距离,从而能够支持更多I/O引脚和更高的每引脚速率。

然而,这种高度集成的设计也带来了挑战,特别是发热问题。为了应对这一挑战,英伟达计划在模块内直接整合冷板,以提升解热能力。这种创新的设计思路旨在确保AI加速器复合体在高性能运行的同时,保持稳定的温度控制。

尽管这一设想令人振奋,但英伟达的技术专家Ian Cutress认为,这一AI加速器复合体的实现仍需时日。他预计,由于英伟达AI GPU订单的庞大需求,对硅光子器件的产能要求极高,只有当英伟达能够确保每月生产超过100万个硅光子连接时,才会考虑转向光学I/O。

垂直芯片堆叠所带来的热效应也是一个亟待解决的问题。Ian Cutress指出,为了克服这一挑战,需要采用更先进的材料和技术,甚至可能在未来出现芯片内冷却方案。因此,他预计这一设想中的AI加速器复合体最早可能在2028至2030年间成为现实,甚至可能更晚。